# Digital System Design

FROM: Walker McGilvary TO: Professor of ELEC 4200 DATE: December 22, 2024 LAB SECTION: Section 001

Final Project - Basic CPU

## Introduction

This project implements a basic CPU (central processing unit) design using Verilog. This CPU has three main modules: **CPU**, **ALU**, and **Seven-Segment-Decoder**. The CPU module is the top-level module which instantiates the ALU and Decoder. Additionally, the CPU cycles through three different states: **FETCH**, **EXECUTE**, and **UPDATE**.

The ALU has two inputs alu\_in1 and alu\_in2, and outputs alu\_out.

The seven-segment-decoder is responsible for outputting the proper seven-segment display LEDs to represent a BCD number.

In addition to the Verilog CPU, I implemented a custom assembly language, which is converted to 16-bit machine code using a Python script. This greatly simplifies the programming process.

## **CPU** Architecture

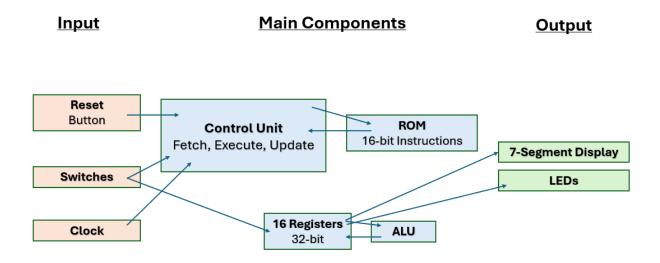

Figure 1: Block Diagram of CPU

The CPU consists of four main components to execute instructions. The Control Unit has three stages to run each line of code. The Program ROM stores up to 256 16-bit instructions that are fetched and decoded by the Control Unit. The registers contains sixteen 32-bit general-purpose registers, which store data for computation and results. The ALU (Arithmetic Logic Unit) performs operations like addition, subtraction, and equality comparison.

Input is handled through the FPGA's switches, which can load values directly into registers. Output is managed through a 7-segment display controller that shows register values. The entire system is synchronized by the clock signal and can be reset to its initial state.

This architecture, while simple, provides all necessary components for a functional CPU capable of

executing basic programs and algorithms.

## **Key Features**

Key features include:

- 32-bit registers

- 16 general-purpose registers

- Three-stage execution cycle:

- Fetch: Load current instruction from program memory

- Execute: Perform instruction operation (ALU, register transfer, etc.)

- Update: Increment program counter and update outputs

- Opcodes:

- MOV: Register-to-register transfer

- LOAD: Load immediate 12-bit value

- ALU operations: Addition, subtraction, equality comparison

- Branch operations for program flow control

- I/O instructions for FPGA board interaction

- Custom assembly language with Python-based assembler

- FPGA Integration:

- 7-segment display output

- Switch inputs

- LED outputs for debugging

- 256 lines of instructions, each 16-bit

## Limitations

Because this CPU design is very simple, there are some limitations:

- Memory Constraints:

- Maximum program size of 256 instructions

- Only 16 general-purpose registers

- Instruction Limitations:

- LOAD instruction can only handle 12-bit immediate values, despite having 32-bit registers

- Basic branching (only branch\_if\_zero implemented)

- Performance:

- Three clock cycles required per instruction

- No pipelining or optimization features

However, despite these limitations, this CPU is still very powerful.

## Assembly Language and Parser

The CPU uses a custom assembly language, which greatly simplifies the programming of the CPU. The instruction set consists of seven opcodes. The first three bits (15-13) of each instruction specify the opcode, with the remaining bits used for opcode-specific instructions.

#### Instruction Format and Opcodes

- MOV (000): Copy value between registers

- Example: mov 1 2 // Copy from register 1 to register 2

- LOAD (001): Load 12-bit immediate value into register

- Example: load 0 5 // Load value 5 into register 0

- ALU (010): Perform arithmetic operation

- Example: alu 0 1 add // Add registers 0 and 1

- SAVE\_ALU (011): Store ALU result in register

- Example: save\_alu 2 // Save ALU result to register 2

- LOAD\_INPUT (100): Read from FPGA switches

- BRANCH\_IF\_ZERO (101): Conditional branching

- END (111): Terminate program execution

#### Python Parser

A Python script handles the conversion from assembly language to machine code. The parser:

- Reads assembly code line by line

- Ignores comments (lines starting with //)

- Converts each instruction into its 16-bit binary representation

- Handles different instruction formats based on opcode

- Outputs machine code to a program.mem file

| NCE                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| first variable                                                                                                                                        |

| second variable                                                                                                                                       |

| constant = 0                                                                                                                                          |

| OUTPUT CURRENT NUMBER (register 15 goes to basic_output)                                                                                              |

| add first & second variables                                                                                                                          |

| save output to the fourth register                                                                                                                    |

| set first variable = second variable                                                                                                                  |

|                                                                                                                                                       |

| set second variable = current fibbonaci number                                                                                                        |

| // loop indefinitely (reg 0 is a constant equal to 0) $% \left( $ |

| <pre>// it should never here, but if it does its bugged</pre>                                                                                         |

|                                                                                                                                                       |

|                                                                                                                                                       |

For example, the Fibonacci sequence can be programmed with this assembly language:

The programming process is seen in the figure below:

Figure 2: Fibonacci Sequence - Python Parser, Assembly Code, and Machine Code

## Simulation

Using a testbench, the CPU operation can be tested in Vivado.

| ຊ 🖬 🔍 ຊ 💥 🖌 ୶             | 14 H 12 27 H                           | - Fe  | +F          | -[            | × H              |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        |         |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

|---------------------------|----------------------------------------|-------|-------------|---------------|------------------|---------|---------|---------------|---------|--------------|--------------|---------------|--------|-----|------------|----------------|----------------|-------------|----------------|--------|---------|---------------|--------------|---------|---------------|---------|-----------------------------------------------|--------------|----------------|--------|------|-------------|--------|---------------|-------|--------------|----|

|                           |                                        |       |             |               | ,                |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        |         |               |              |         |               |         |                                               |              |                |        |      |             |        | _             | _     | _            |    |

| Name                      | Value                                  |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        |         |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

|                           | value                                  | 0.000 | ns          | 50.0          | 30 ns            | 100.000 | 0 ns    | 150.000       | Ins     | 200.00       | 10 ns        | 250.0         | 100 ns | 300 | 000 ns     | 350.1          | 000 ns         | 400.00      | 0 ns           | 450.00 | 10 ns   | 500.0         | 10 ns        | 550.00  | 0 ns          | 600.000 | ns                                            | 550.00       | 0 ля           | 700.00 | 0 ns | 750.00      | 0 ns   | 800.000       | ns 85 | 0.000 na     |    |

| 4 dk                      | 0                                      |       |             |               |                  |         |         |               |         |              |              | циш           |        |     |            | μιιι           |                |             |                |        |         | , uuuu        |              | JUUUU   |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| reset                     | 0                                      |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        |         |               |              |         | _             |         |                                               |              |                |        |      |             |        |               |       |              |    |

| opcode[2:0]               | 2                                      | ×     | <u> </u>    | _^_           | <u>(2)3)</u>     |         |         |               | · · · · |              |              | <u> </u>      |        |     |            |                |                |             |                |        |         |               |              |         |               |         | <u>, , , , , , , , , , , , , , , , , , , </u> | <u> </u>     |                |        |      |             |        |               |       |              | -  |

| <sup>g</sup> pc[31:0]     | 4                                      | 0     | <u>_X_X</u> | <u>zX z X</u> | <u>4 X 5 X 6</u> | X_XX_   | 2 (3)   | <u>_X_X</u>   | لتلا    | <u>X 2</u> ) | <u>a</u> (a) | ( <u>5)(6</u> |        | 2 3 | XXX        | <u> «X z X</u> | <u>X = X 3</u> | <u>X_X_</u> | <u>X 6 X 7</u> | (X2)   | (1)     | <u>5 (6</u> ) | <u>-XX</u> - | _X_X    | <u>_X_X</u> _ | XIX     | 2 3                                           | <u>(4)(5</u> | <u>X 6 X 7</u> | XX2    |      | 5 6         | CXX.   | 2 <u>X3X4</u> | X=X=X | <u>2XX</u> 2 | X  |

| branch_destination[7:0]   | 10                                     | xx    | 01          |               | χ. χ. οο         |         |         | <u>X.</u> ( 0 | 0 X .   |              |              | 00            |        |     | . X. X. o  | 0 X            | $\infty$       |             | 00 X.          | XX     |         | X 00          |              | $\odot$ | . 00          |         |                                               |              | 00 X.          |        |      | <u>)</u> 00 |        |               | 00    |              |    |

| basic_out[31:0]           | 00000090                               | ×2    | xoxo        |               |                  |         | 00000   | 001           |         |              |              | 000           | 00002  |     | <u>)</u> ( | 000000         | 13             |             | 000000         | 05     |         | 000           | 30008        |         | 00            | 000004  |                                               |              | 00000          | 015    |      | 000         | 000022 |               | 000   | 00037        |    |

| current_instruction[15:0] | 4020                                   | 20000 |             |               | $\infty$         |         |         |               |         |              |              | XX            |        |     |            |                | $\square$      |             |                | X      |         |               |              | $\odot$ |               |         |                                               |              |                |        |      | XIX         |        |               |       |              |    |

| registers[0:15][31:0]     | 00000090,000000e9,0                    | x     |             | . 0           | 0                | . 0000  | 00001,. |               | . 0     | 000          |              |               | . 000  | 0   | 0          | . 0            | 000            | 0           |                | 0000   |         |               | . 0000       |         |               | . 000   |                                               | 0            |                | 0000   | 0    |             | . 0000 |               |       | . 0000.      |    |

| > 😻 [0][31:0]             | 144                                    | x     |             |               |                  | 1       |         |               | X       | -            | 2            | Х             |        | 3   |            | X              | 5              |             |                |        | 8       |               |              | 13      |               | $( \ )$ | 21                                            |              |                | -      | 34   | )           |        | 55            | X     |              | 89 |

| > 😻 [1][31:0]             | 233                                    | x     |             |               | 1                | _X      | 1       | 2             | _X      |              | 3            |               | χ_     |     | 5          | X              |                | 8           | )              |        | 13      |               | X            | 21      |               | X       |                                               | 34           | X              |        | 55   |             | (      | 89            |       | Χ            | 1  |

| > 😻 [2][31:0]             | 00000000                               | XXX0  | XXXXX       |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | 0000000 | 0             |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [3][31:0]             | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                | 000000 | CK.     |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [4][31:0]             | 233                                    |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        |         |               |              |         |               |         | 4                                             |              |                |        |      |             | 8      | 9             |       | 144          |    |

| > 😻 [5][31:0]             | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                | 000000 | 00      |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [6][31:0]             | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                | 000000 | CX.     |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 💴 [7][31:0]             | X0000000K                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                | 000000 | x       |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [8][31:0]             | XXXXXXXXXXX                            |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | CK      |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [9][31:0]             | XXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXXX |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | α       |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [10][31:0]            | XXXXXXXXXXXX                           |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                | 000000 | OK      |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [11][31:0]            | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | x       |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [12][31:0]            | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | ox.     |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [13][31:0]            | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | CX:     |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 😻 [14][31:0]            | X0000000X                              |       |             |               |                  |         |         |               |         |              |              |               |        |     |            |                |                |             |                |        | CX.     |               |              |         |               |         |                                               |              |                |        |      |             |        |               |       |              |    |

| > 🛡 [15][31:0]            | 00000090                               |       |             |               |                  |         | 000000  | 01            |         |              |              | 0000          | 0002   |     | 00         | 00000          | _              |             | nnnnnn         | 5      |         | 0000          | 1009         |         | 000           | 00004   | -                                             |              |                | 5      |      | 0000        | 0022   |               | 0000  | 0022         |    |

Figure 3: Fibonacci Sequence - Vivado Simulation

The figure above shows the Vivado simulation of the Fibonacci Sequence program. Key observations:

- 3 clock cycles per line of code (corresponds to 3 CPU states)

- Registers 0 and 1 are added, and register 4 acts as an accumulator of the sequence.

- Register 15 is output to the 7-segment display.

- The program keeps looping, which is due to the branch\_if\_zero statement.

The figure below shows the simulation of a countdown program:

| Name                          | Value             | 0.000 ns |         |          | 200.000 ns  |         | 400.     | 000 ns     |           | 600.00    | 0 ns       |                | 800.000 n   | * ,     |       | 1,000.0 | 10 ns |            | 1,200.000 ns    |                  | 1,400.000 ns      |        |

|-------------------------------|-------------------|----------|---------|----------|-------------|---------|----------|------------|-----------|-----------|------------|----------------|-------------|---------|-------|---------|-------|------------|-----------------|------------------|-------------------|--------|

| li cik                        | 1                 |          | nnnnnn  | TTT      |             | inninni | TTT      |            |           |           |            | <b>i</b> nnnnn |             |         |       |         | nnnn  |            |                 |                  |                   |        |

| 🐸 reset                       | 0                 |          |         |          |             |         |          |            |           |           |            |                |             |         |       |         |       |            |                 |                  |                   |        |

| > ♥ opcode[2:0]               | 7                 | X 1      | 2)      | 3 2      | 3 5 1       | 2)      | 3)2)     | 3)(5)      | 1 2       | 3 2 3     | X          | 1 2            | 3 2 3       |         | 1 2   | 3 (2)   | 3 5   | 1)         |                 | 7                |                   |        |

| > 😻 current_instruction[15:0] | ****              |          |         | ·· )(··· |             |         |          | )()(       |           |           |            |                |             |         |       |         | -)    | X •• X     |                 | £1113            |                   |        |

| v v registers[0:15][31:0]     | 0000000,0000001,0 |          |         | 000      | 00000004,00 | 0000    | 00000003 | ,00000001, | 0000 X    | 00000002, | 00000001,0 | 000            | 00000001,00 | 0000001 | ,0000 | 000     | 000   | 00000000,0 | 0000001,0000000 | 0, X00000000, 00 | XXXXXX,00000001,X | xxxxxx |

| > 😻 [0][31:0]                 | 0000000           | 0        | 0000005 | X        | 00000004    | X       |          | 00000003   | χ         |           | 00000002   |                | 0           | 000000  | 1     | X       |       |            | 00              | 00000            |                   |        |

| > 👽 [1][31:0]                 | 00000001          | xxxx (   |         |          |             |         |          |            |           |           |            |                | 00000001    |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [2][31:0]                 | 00000000          | X000000X |         |          |             |         |          |            |           |           |            |                | 000000      | 000     |       |         |       |            |                 |                  |                   |        |

| > 😻 [3][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [4][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              |             |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [5][31:0]                 | 00000001          |          | x000000 |          |             |         |          |            |           | 000000    | 00         |                |             |         |       |         |       |            |                 | 00000001         |                   |        |

| > 👽 [6][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [7][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              |             |         |       |         |       |            |                 |                  |                   |        |

| > 👽 [8][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              |             |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [9][31:0]                 | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [10][31:0]                | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 0000000     |         |       |         |       |            |                 |                  |                   |        |

| > 👽 [11][31:0]                | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [12][31:0]                | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 👽 [13][31:0]                | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              |             |         |       |         |       |            |                 |                  |                   |        |

| > 👽 [14][31:0]                | X0000000X         |          |         |          |             |         |          |            |           |           |            | x              | 000000      |         |       |         |       |            |                 |                  |                   |        |

| > 😻 [15][31:0]                | 00000001          |          |         |          |             |         |          |            | XXXXXXXXX |           |            |                |             |         |       |         |       |            |                 | 00000001         |                   |        |

- Register 0 starts at 5

- Register 0 decrements to 0.

• When the register reaches 0, the end opcode is read, and the program is finished.

This program was simply programmed with the alu 0 1 sub operation (subtract 1 from register 0).

## Challenges of FPGA Integration

Next, with the logical verification of the CPU operation (testbench simulations), the CPU will be tested on the FPGA hardware. Because of how Vivado synthesizes and implements the Verilog code, this process took a lot of debugging to achieve correct operation on the FPGA board.

The largest challenge was the 7-segment display clock. The 7-segment display shows multi-digit numbers by quickly rotating between digits. Each digit is briefly lit up in sequence, cycling fast enough that the human eye perceives all digits as continuously lit. This required a separate clock divider to control the display's switching speed.

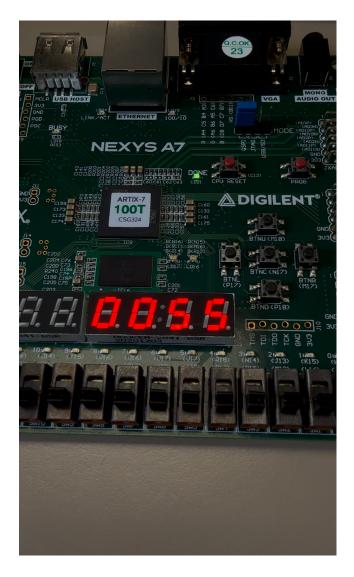

However, because of the separate clock and clock divider, Vivado didn't synthesize this as expected. When the 7-segment display clock was finally working, I was happy to find that the CPU synthesized perfectly, and could run counter programs, the Fibonacci program, and an addition program (using switches as inputs).

Figure 5: 11th Digit in Fibonacci Sequence

As seen above, the Fibonacci Sequence program worked as intended on the hardware. After many clock cycles, the digit 55 is displayed on the 7-segment display.

## Conclusion

This concludes my Final Design Project for ELEC 4200 - Digital System Design. I implemented a basic CPU, written in Verilog. While simple, this CPU is very powerful, and has enough opcodes to run almost any algorithm. The multi-cycle design, with its Fetch, Execute, and Update stages, allow for a fully functional CPU. The instruction set, though minimal, supports essential operations like data movement, arithmetic, branching, and I/O interaction.

The project combines Verilog HDL, custom assembly language development, and practical FPGA implementation. Working example programs, including the Fibonacci sequence and switch-input calculator, prove the CPU's computational capabilities. Despite limitations like 12-bit immediate values and 256instruction memory, the design is Turing complete and should be able to run almost any algorithm.

The project code is on GitHub: https://github.com/TheSlabby/minimal-cpu